用于高功率和高頻應用的最有前途的器件之一是 SiC MOSFET?2,3 它支持更高的結溫,其特點包括低導通電阻和更高的開關?SiC MOSFET 允許構建具有更高功率密度和更高效率的轉換器?然而,SiC MOSFET 的廣泛采用受到其開關損耗的限制?大部分損耗發(fā)生在開啟階段,如器件數據表和報告測試結果所示?

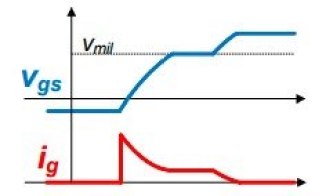

SiC MOSFET 的開關性能由柵極驅動控制?電壓源柵極驅動 (VSG) 是 MOSFET 中使用最廣泛的結構,因為它成本低且結構簡化?9-13 隨著柵極電流的降低,可以看到柵極電壓上升?當米勒平臺現象發(fā)生時,這種上升變得恒定;當柵極驅動輸出電壓處于恒定速率時會發(fā)生這種情況?1 整個過程如圖 1所示 ?為了提高功率器件的開關速度,需要在發(fā)生開關瞬態(tài)時提高柵極電流14–17,為此,設計了電流源柵極?原始文章可以在這里找到 ?

圖 1:開啟瞬態(tài)期間的柵極電流

電荷泵柵極驅動 (CPG)

有限的柵極電流是提高 SiC MOSFET 開啟開關速度的原因?為了找到解決方案,需要進一步研究在典型 VSG 的導通瞬態(tài)過程之間影響柵極電流的因素?SiC MOSFET 的柵極電壓額定值為 20 V?1 柵極驅動器可滿足開關過程中的兩個主要要求:首先,柵極驅動器應提供足夠量的柵極電流,以減少開關過程中的開關時間?開關瞬態(tài)階段?其次,柵極驅動器應該能夠在瞬態(tài)和穩(wěn)態(tài)期間保持柵極電壓處于受控狀態(tài)?(君芯-MOS)

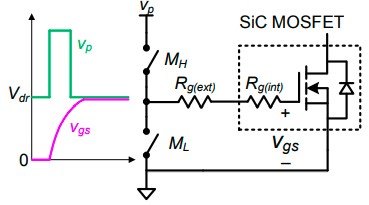

柵極電壓應保持在 MOSFET 的額定值以下?1 由于第二個條件,已經注意到不能增加柵極驅動器電源電壓? 圖 2 描繪了柵極驅動器的理想電源電壓?為了增加電壓量,需要更多的變壓器和電源,這最終會增加與柵極驅動相關的成本和復雜性?18 電壓偏移需要精確的控制信號來避免柵極過壓,這不僅增加了電路的復雜性,而且不能自適應地適應不同的負載和總線電壓條件,其中開關瞬態(tài)時間會發(fā)生變化?1

圖 2:具有理想電壓電源的柵極驅動

CPG的工作原理

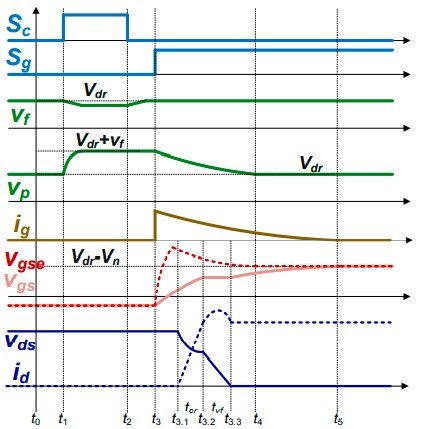

典型的導通開關周期有五種模式? 圖 3 顯示了在此過程中形成的波形?當導通瞬態(tài)開始時,操作如下:

子區(qū)間 1 (t0–t1)

子區(qū)間 2 (t1–t2)

子區(qū)間 3 (t2–t3)

子區(qū)間 4 (t3–t4)

子區(qū)間 5 (t4–t5) 1

典型的 VSG 和建議的 CPG 具有類似的關斷過程,因為導通損耗遠大于關斷損耗?1

圖 3:CPG 波形

控制信號產生

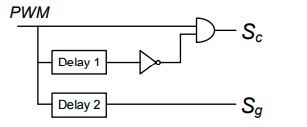

建議的 CPG 需要兩個控制信號,并且可以通過 PWM 輸入信號和幾個邏輯門的組合輕松確認?圖 4顯示了對控制提議的 CPG 的基本原理的確認 ?延遲單元基本上可以使用具有各種值的 RC 濾波器來執(zhí)行?1

圖 4:CPG 控制邏輯實現

提議的 CPG 的好處和挑戰(zhàn)

優(yōu)點包括在開啟階段的低開關損耗,因為在開啟開關瞬態(tài)期間為柵極電容器充電的柵極電流較高?與傳統(tǒng) VSG 相比,這是通過泵柵極驅動輸出電壓的電壓實現的?1 已泵送的充電電壓降低回正常柵極電源電壓?這最終將避免任何類型的過度充電?1 SiC MOSFET 的開啟開關速度可以通過改變外柵極電阻輕松調整?1 因此,用建議的 CPG 替換電源轉換器中的傳統(tǒng) VSG 很方便?它的挑戰(zhàn)包括電荷存儲電容器電壓和更高的 dV/dt?

參數設計

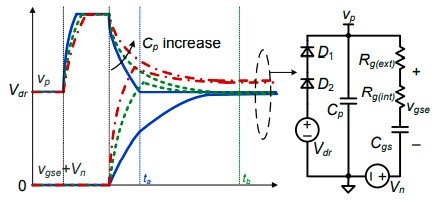

在設計建議的 CPG 時,選擇合適的電容 C P很重要? 圖 5 顯示了虹吸電壓 V P 和外門對地電壓 (V gse + V n ) 與不同 C P的波形?1 在導通瞬態(tài)期間,C P 將電荷轉移到 C GS?

圖 5:不同 Cp 的開啟階段電壓波形

實驗結果

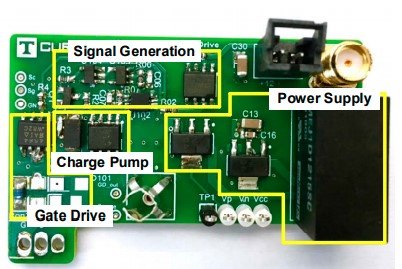

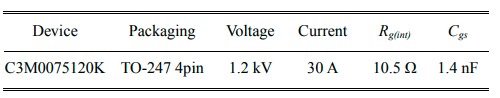

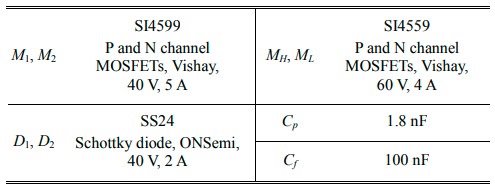

在 Wolfspeed 最先進的芯片技術的幫助下,使用 SiC MOSFET 對建議的 CPG 進行了測試,如圖 6所示 ? 表 1 和表 2 表示與 CPG 相關的參數和 MOSFET 的特性?

圖 6:CPG 的原型

表 1:碳化硅 MOSFET 的特性

表 2:柵極驅動參數

結論

本文介紹了一種能夠改善 SiC MOSFET 導通開關損耗的 CPG 驅動器?已對建議的 CPG 和傳統(tǒng)的 VSG 進行了比較?該實驗的結果表明,所提出的 CPG 的導通損耗值降低了 71.7%,而滿載條件下的開關時間降低了 67.4%?